# Analog Front End for the fiber tracker in Dzero

### I can tell you about the Dzero electronics, but I do not know what you want and/or need.

### THIS IS NOT A LECTURE

### LETS TALK

Outline

What

How

Why

Lessons

learned

5/22/2010

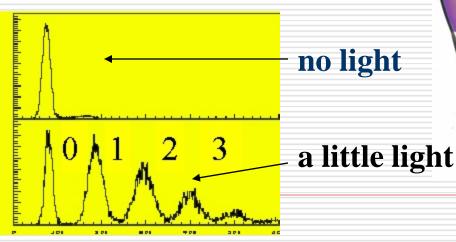

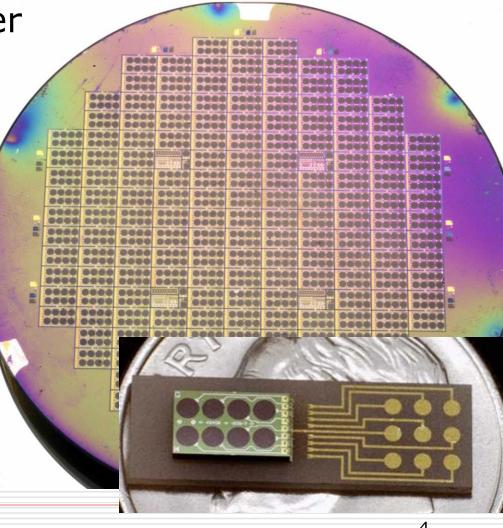

# VisibleLightPhotonCounter very high QE good gain low noise makes fiber tracker possible!

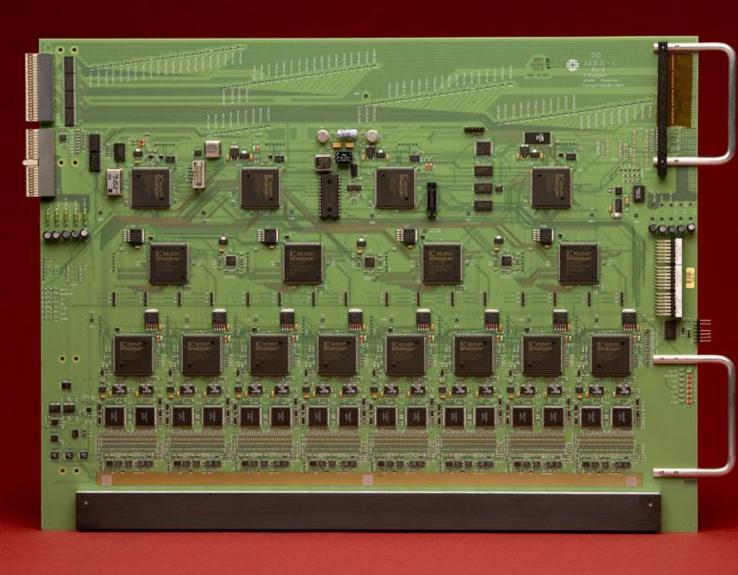

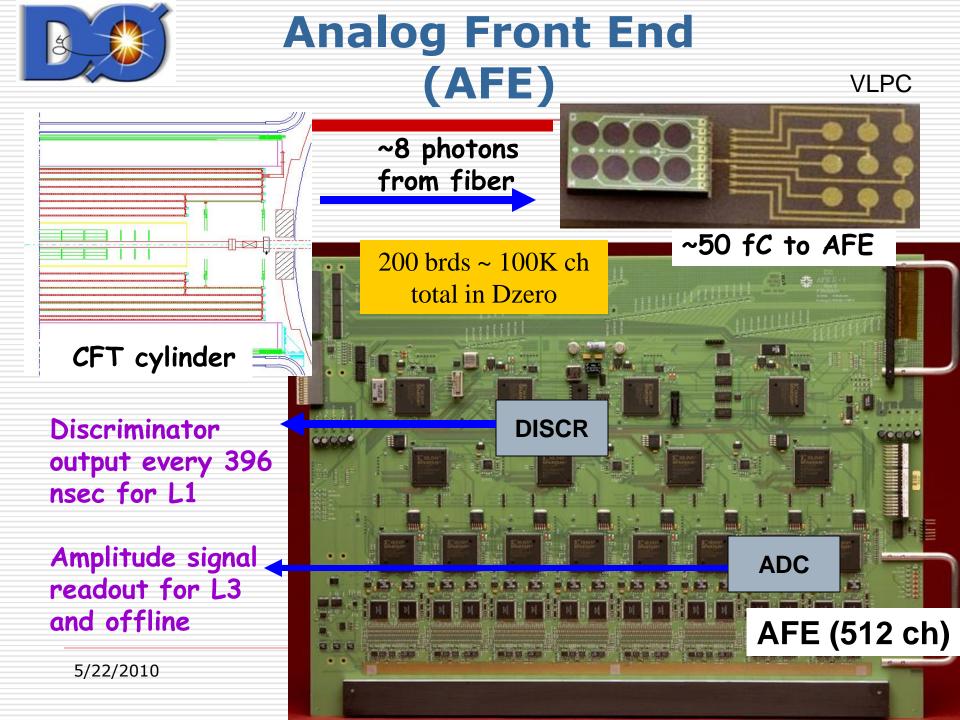

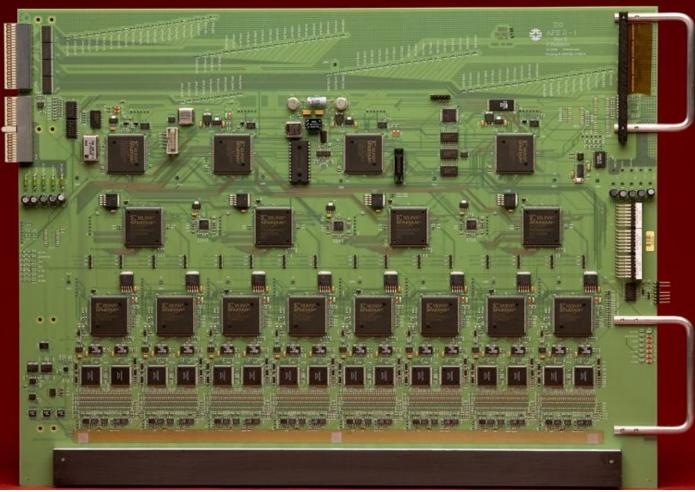

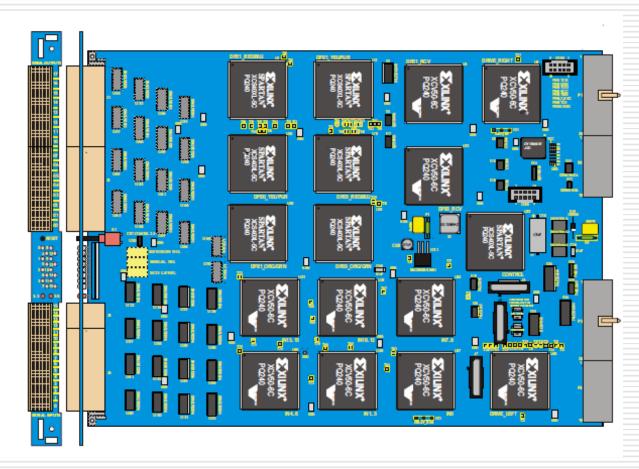

### Analog Front End (AFE)

#### 3 main responsibilities

- 1. Care and feeding of the VLPCs (via slow control)

- Bias (±40mV)

- Temperature control (±0.05K)

- 2. Hit/no hit decision to the trigger system every crossing, every fiber.

- Used in forming Level 1 decision

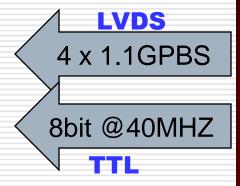

- 512 ch/board, every BX ( max 485 MB/s)

- 3. Amplify VLPC signals, digitize to 8 bits, zero suppress and readout every on L1 accept

- max 40 MB/s

- Readout via same system as silicon strip vertex detector

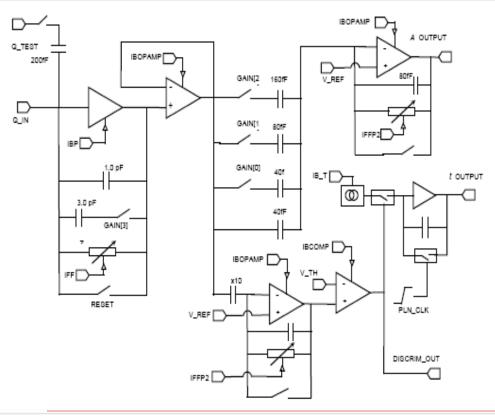

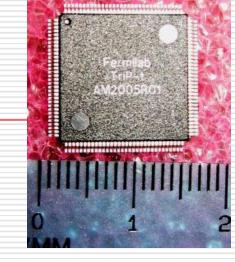

TriP-t

AFE is designed around the TriP-t

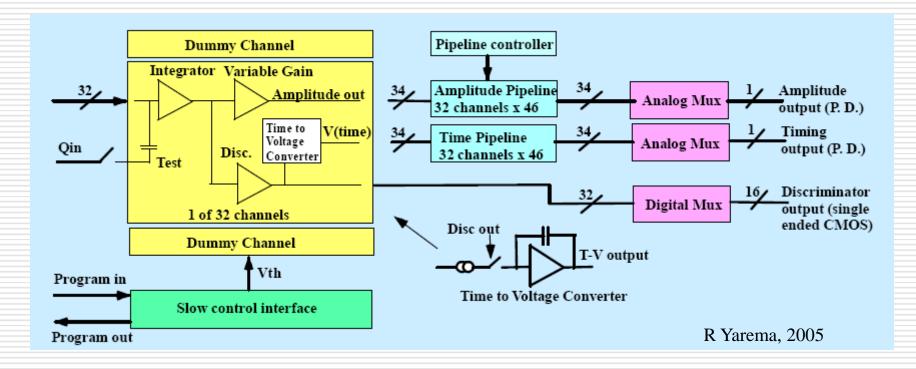

Trigger and Pipeline – with timing

- 32ch/chip: discr,48 cell analog pipeline ea.

- 0.25um CMOS manufactured by TSMC

- TriP-t ASIC designed specifically for Dzero VLPC based detectors: CFT, CPS, FPS

- TriP-t designed by Fermilab ASIC group, A. Mekkaoui lead designer

- Fermilab has a strong ASIC group, lots of experience, wide range of capabilities

slow control from FPIX, pipeline from SVX4

🗅 TriP-t

TriP-t

#### TriP-t

DC stable wide dynamic range high bandwidth low noise

Very flexible: adjustible gain adjustible bandwidth

5/22/2010

#### Some parameters

integration gate: 50ns to 20us, controlled by external clock

- gain: 12mv/fC to 0.37mv/fC, switch set

- pipeline depth 1 to 47, dead-timeless

- noise: ~1fC for 40pF input capacitance

- Iow power: 6.5mW/ch

- discriminator thresh: 1/chip, 10fC to 300 fC

- TDC: 1ns resolution

for more info: rubinov@fnal.gov

#### TriP-t ideas:

- "keep it simple"

- do only what can not be done with commercial ICs ADC is external, zero suppression in external FPGA

- "keep it flexible"

- internal DACs (set via serial interface) can be used to adjust bandwidth, power, gain flexible clocking scheme, driven by FPGA

- "ease of use"

temperature compensated to first order features to support testing, calibration

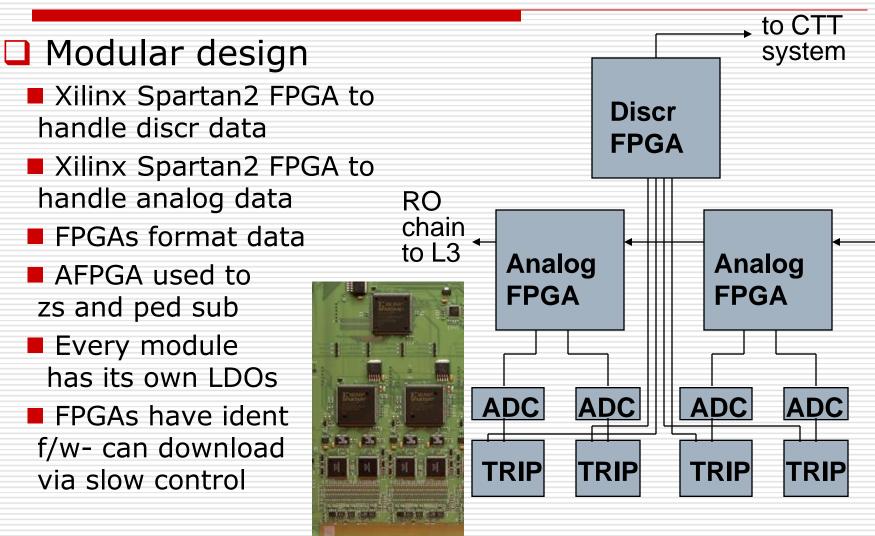

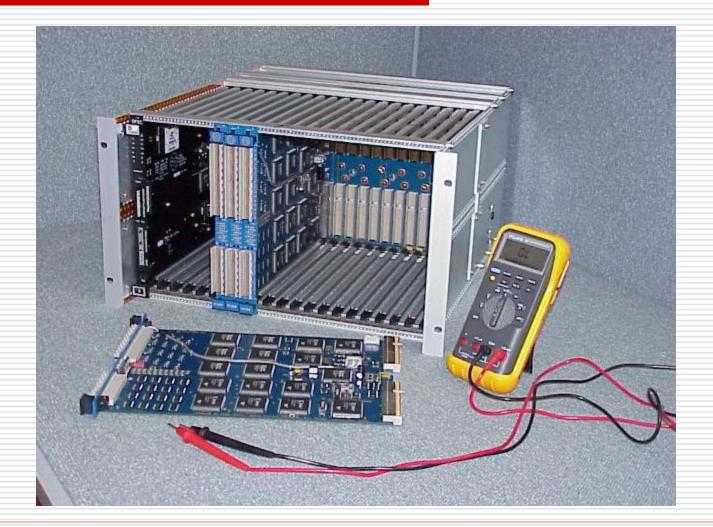

# **AFE board design**

### **Data Flow**

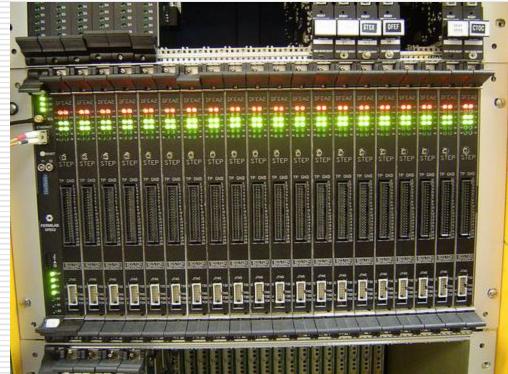

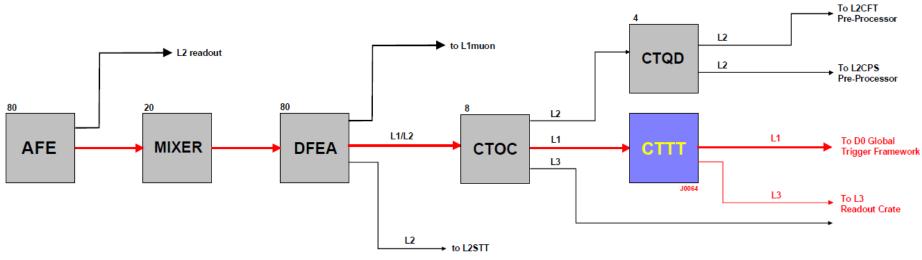

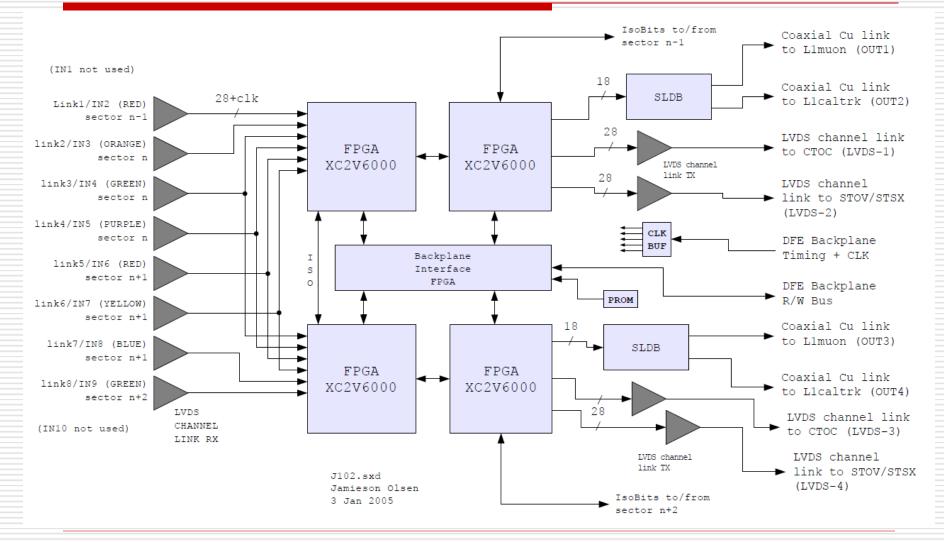

# **Central Track Trigger**

Based on DFEA2 Upgraded for RunIIb

#### **L1CTT CHAIN DIAGRAM**

5/22/2010

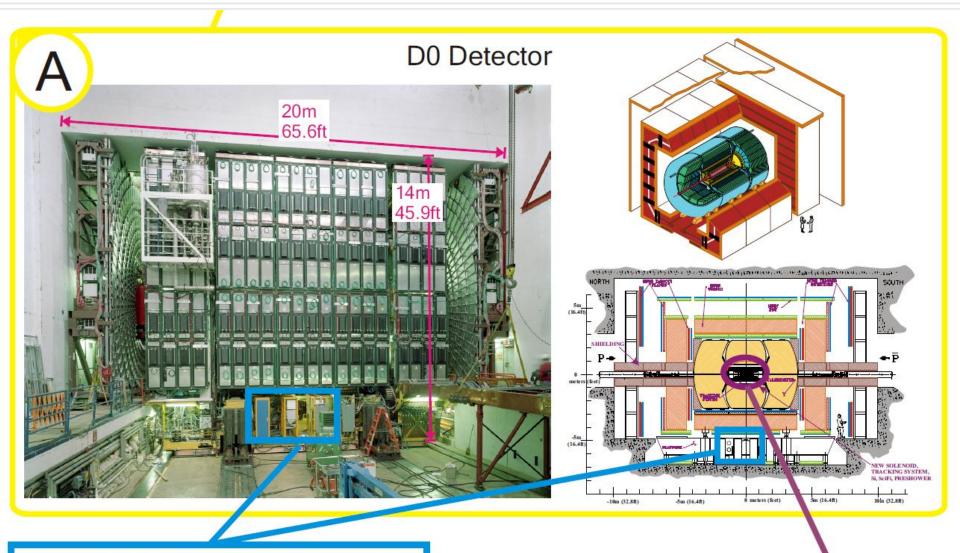

## The whole picture

#### **Central Fiber Tracker Electronics**

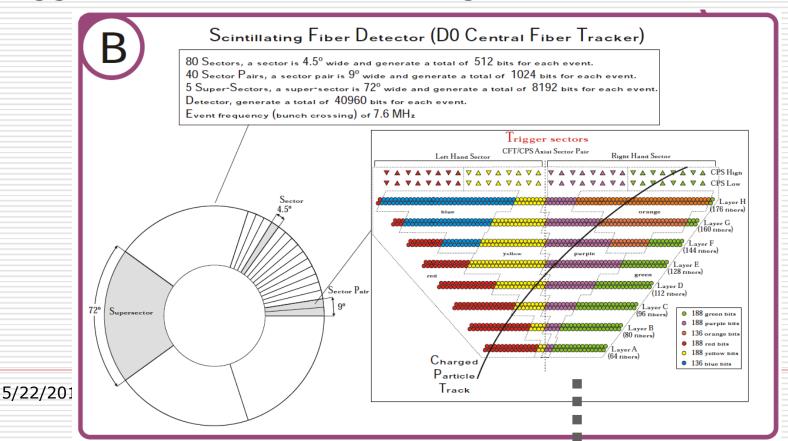

#### Horrible mapping problem:

### Fiber ribbons (and AFE) are organized in cylinders Trigger needs to work in wedges

18

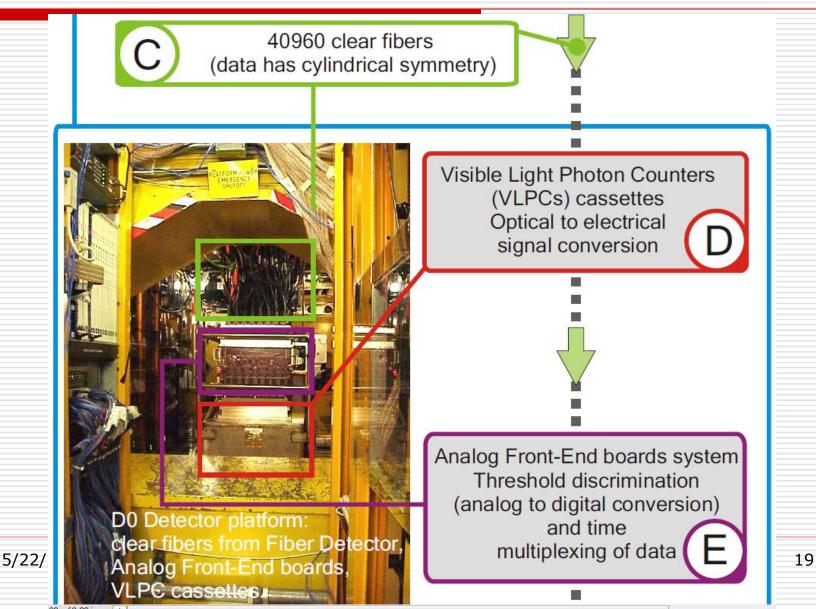

## **Overview (cont)**

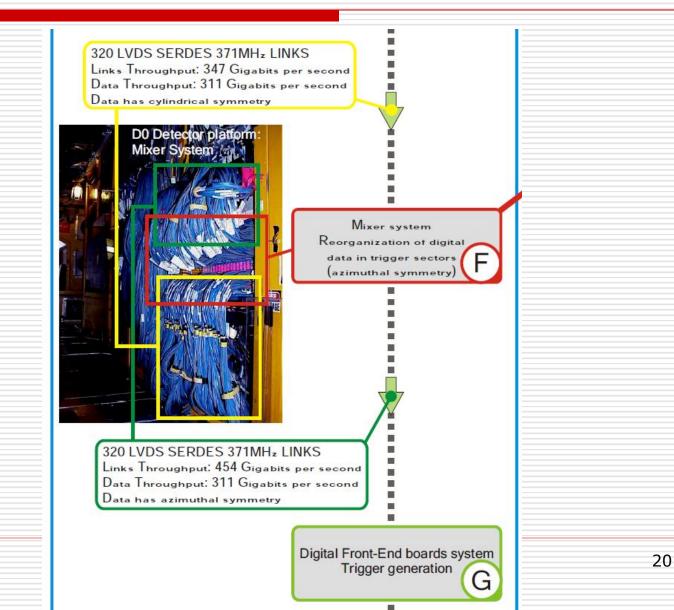

## **Overview (cont)**

5/22/2010

The MIXER is a brilliant bit of engineering

But its getting a bit long in the tooth

It's the only part of the system that is not version II

Dzero is a complex system

- □ some parts are easy to repurpose

- some parts are not

- The largest investment, BY FAR, is intellectual

- □ hardware is a drop in the bucket by comparison

- You can probably reuse much of the hardware

# Don't underestimate the re-engineering required

### SPARE SLIDES AFTER THIS POINT